根據韓國半導體工程師協會發布的《半導體技術路線圖2026》,全球先進邏輯製程未來15年將持續微縮,從目前規劃中的2奈米節點,推進至2040年的0.2奈米,正式跨入埃米(Å)世代。報告指出,隨著線寬微縮逐步逼近物理極限,製程演進將不再單靠微影技術,而是轉向結構、材料與系統層級的整體革新。

路線圖顯示,產業預期在2031年前後進入1奈米世代,即使0.75NA EUV可在2030年前後持續支撐製程微縮,但以光刻為核心的線寬縮小將逐漸遭遇瓶頸,未來競爭焦點將轉向晶片架構與系統設計。

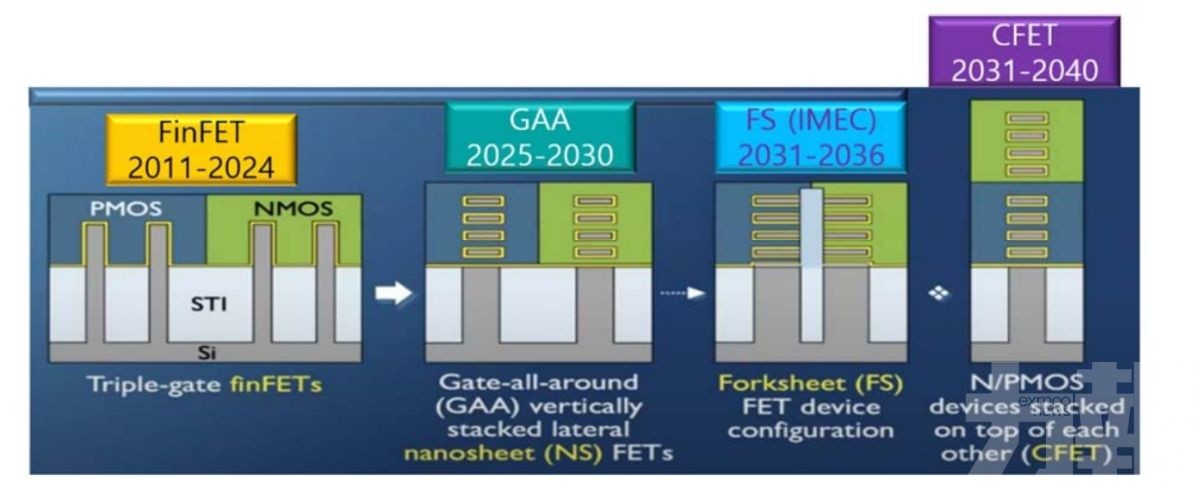

為延續效能提升,電晶體結構將由FinFET演進至GAA,並進一步發展為CFET等三維架構,透過PMOS與NMOS垂直堆疊突破密度限制,配合單晶3D製程及由DTCO走向STCO的設計思維,提升整體效能。

在記憶體方面,DRAM與邏輯製程同步邁向3D化,HBM堆疊層數與頻寬將大幅提升,2040年頻寬可望達128 TB/s;NAND Flash則持續以增加層數換取密度,最高挑戰2,000層。整體而言,半導體產業正加速邁入「超越摩爾定律」的新時代。(編輯部)